# Tensor Operations on Edge Devices

# BACHELORARBEIT

zur Erlangung des akademischen Grades Bachelor of Science (B. Sc.) im Studiengang Informatik

FRIEDRICH-SCHILLER-UNIVERSITÄT JENA Fakultät für Mathematik und Informatik

eingereicht von Till Billerbeck geb. am 26.08.1999 in Dresden Betreuer: Prof. Dr. A. Breuer Jena, 30.07.2025

# Kurzfassung

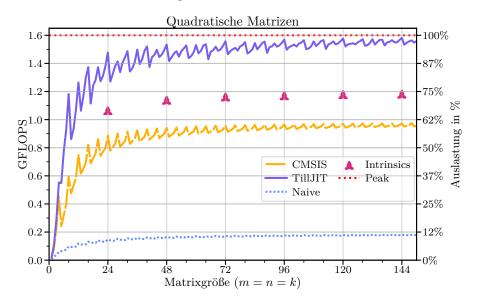

Effiziente Berechnung von Matrixmultiplikation ist seit langer Zeit ein stark erforschtes Feld. Die Forschung hat sich zumeist auf x86-64, Aarch64, GPUs und spezialisierte Hardware konzentriert. Für die neue Helium-Erweiterung (auch M-Profile Vector Extension / MVE genannt) der Cortex-M-Prozessorreihe existiert zum derzeitigen Stand nur eine Referenzbibliothek von Arm zur Matrixmultiplikation. In dieser Arbeit werde ich die Helium-Erweiterung und den Cortex-M55 detailliert beschreiben, um mithilfe der daraus gewonnenen Erkenntnisse eine Bibliothek zur Matrixmultiplikation zu implementieren. Dazu wird ein Just-in-Time-Compiler entwickelt, der Kernel zur Matrixmultiplikation erzeugt. Im Vergleich zur Referenzbibliothek von Arm wird ein Geschwindigkeitszuwachs von durchschnittlich 94% erzielt und 99% der theoretisch erreichbaren maximalen Leistungsfähigkeit des Prozessors erreicht.

# Inhaltsverzeichnis

| 1.         | Einführung                                            | 5       |  |  |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------|---------|--|--|--|--|--|--|--|--|--|

| 2.         | Embedded Hardware I: Arm M-Profil                     | •       |  |  |  |  |  |  |  |  |  |

|            | 2.1. Cortex M-Profil Prozessorreihe                   | (       |  |  |  |  |  |  |  |  |  |

|            | 2.1.1. Cortex-M55                                     | (       |  |  |  |  |  |  |  |  |  |

|            | 2.1.2. Weitere Prozessoren mit M-Profil               | 10      |  |  |  |  |  |  |  |  |  |

|            | 2.2. Armv8.1-M-Profil                                 | 10      |  |  |  |  |  |  |  |  |  |

|            | 2.2.1. Helium-Erweiterung                             | 1       |  |  |  |  |  |  |  |  |  |

|            | 2.2.2. Maskierung                                     | 1!      |  |  |  |  |  |  |  |  |  |

|            | 2.2.3. Low Overhead Loops                             | 10      |  |  |  |  |  |  |  |  |  |

|            | 2.2.4. Tail-Predication                               | 19      |  |  |  |  |  |  |  |  |  |

|            | 2.3. Arm Microcontroller Software-Stack               | 19      |  |  |  |  |  |  |  |  |  |

| 3.         | Embedded Hardware II: Alif E7 Board                   | 20      |  |  |  |  |  |  |  |  |  |

| ٠.         | 3.1. Rechenleistung                                   | 20      |  |  |  |  |  |  |  |  |  |

|            |                                                       |         |  |  |  |  |  |  |  |  |  |

|            | 3.2. Speichersystem                                   |         |  |  |  |  |  |  |  |  |  |

|            | 3.2.1. Dauerhafter Speicher – MRAM                    |         |  |  |  |  |  |  |  |  |  |

|            | 3.2.2. Langsamer Speicher - SRAM                      |         |  |  |  |  |  |  |  |  |  |

|            | 3.2.3. Schneller Speicher - Tightly Coupled Memory    | 2       |  |  |  |  |  |  |  |  |  |

| 4.         | Just-In-Time-Kompilierung für Matrixmultiplikation    | 24      |  |  |  |  |  |  |  |  |  |

|            | 4.1. Just-In-Time-Kompilierung auf Cortex-M55         | $2^{2}$ |  |  |  |  |  |  |  |  |  |

|            | 4.2. Umsetzung und Schnittstelle                      | 20      |  |  |  |  |  |  |  |  |  |

|            | 4.3. Instruktionsenkodierung für Matrixmultiplikation | 2'      |  |  |  |  |  |  |  |  |  |

|            | 4.4. Branching und Schleifen                          |         |  |  |  |  |  |  |  |  |  |

| <b>5</b> . | Effiziente Matrixmultiplikation                       |         |  |  |  |  |  |  |  |  |  |

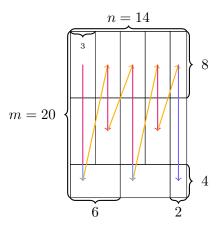

|            | 5.1. Implementierung des Microkernels für Helium      | 30      |  |  |  |  |  |  |  |  |  |

|            | 5.2. Abarbeitung der Microkernel                      | 35      |  |  |  |  |  |  |  |  |  |

|            | 5.3. Optimierungen                                    | 3       |  |  |  |  |  |  |  |  |  |

|            | 5.3.1. Überlagerung der Instruktionen                 | 3       |  |  |  |  |  |  |  |  |  |

|            | 5.3.2. Loop Peeling in zwei Schritten                 | 3       |  |  |  |  |  |  |  |  |  |

|            | 5.3.3. Ausrollen der Schleifen                        |         |  |  |  |  |  |  |  |  |  |

|            |                                                       |         |  |  |  |  |  |  |  |  |  |

|            | 5.4. Anpassungen für große Matrizen                   | 3'      |  |  |  |  |  |  |  |  |  |

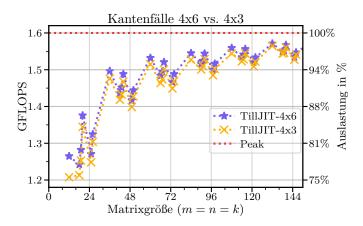

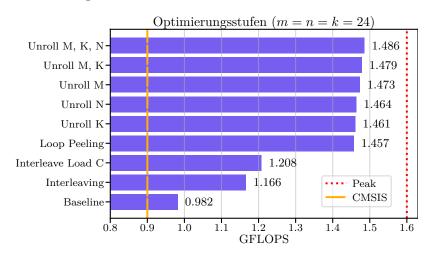

| <b>6</b> . | Ergebnisse                                            | 38      |  |  |  |  |  |  |  |  |  |

|            | 6.1. Vergleichslösungen                               | 38      |  |  |  |  |  |  |  |  |  |

|            | 6.2. Performance                                      | 39      |  |  |  |  |  |  |  |  |  |

| <b>7</b> . | Forschungsstand                                       | 41      |  |  |  |  |  |  |  |  |  |

| 8.         | 3. Zusammenfassung und Ausblick                       |         |  |  |  |  |  |  |  |  |  |

| 1 :4       | teraturverzeichnis                                    | 43      |  |  |  |  |  |  |  |  |  |

|            |                                                       |         |  |  |  |  |  |  |  |  |  |

| An         | nlagen                                                | 4       |  |  |  |  |  |  |  |  |  |

| Ab         | bbildungsverzeichnis                                  | 4       |  |  |  |  |  |  |  |  |  |

| Ta         | abellenverzeichnis                                    | 4       |  |  |  |  |  |  |  |  |  |

| Lis        | stings                                                | 4       |  |  |  |  |  |  |  |  |  |

# Vorwort

An dieser Stelle möchte ich mich für jegliche Hilfe beim Verfassen dieser Arbeit bedanken. Zuerst bei Prof. Dr. Alexander Breuer und Stefan Remke für die Betreuung der Arbeit und zahlreiche Hilfestellungen.

Zudem gilt mein Dank den weiteren Mitgliedern des Scalable Analyses Lab für weitere Anregungen, sowie Daniel Schicker für Motivation und die Beseitigung mehrerer Fehler im vorliegenden Text.

# 1. Einführung

Die effiziente Multiplikation von Matrizen ist seit langer Zeit ein stark erforschtes Thema. Während früher der Fokus auf wissenschaftlichen Berechnungen lag, ist Matrixmultiplikation heutzutage zudem integral für das Training und die Inferenz von Machine Learning-Algorithmen (ML) und Tensoroperationen. Das für Large Language Models (LLMs) unerlässliche Attention-Layer etwa nutzt Matrixmultiplikation [38] und in den Frameworks Tensor Processing Primitives (TPP) [19] und Tensor Operator Set Architecture (TOSA) [13] ist Matrixmultiplikation als unerlässliche Primitive zur Berechnung von ML-Modellen integriert.

Zugleich werden neue Anwendungsgebiete erschlossen, in denen der Einsatz von leistungsstarken Systemen nicht möglich ist, aber trotzdem ML-Anwendungen mit schneller Reaktionszeit und teilweise ohne Internetzugriff ausgeführt werden. Somit ist es meist nicht möglich, die anfallenden Anfragen an einen leistungsfähigeren Server zu übermitteln [39]. Auf diesen "Edge Devices" ist dann häufig eine energiesparende CPU verbaut, der die Fähigkeiten zum Ausführen eines kompletten Betriebssystems fehlen, die aber trotzdem die Anfragen bearbeiten muss und leistungsstark genug sein muss, die Inferenz für einige ML-Anwendungen auszuführen. Für den Anwendungsfall der besonders ressourcenbeschränkten Systeme hat Arm die Cortex-M-Prozessorfamilie entwickelt.

Da SIMD-Instruktionen, welche ansonsten auf anderen CPUs mittels Erweiterungen wie Neon oder AVX-512 bereitgestellt werden, auf Cortex-M Prozessoren bisher auf eine Registergröße von 32 Bit beschränkt waren und nur mit Integerwerten funktionierten, war die erreichbare Leistung für ML-Anwendungen aufgrund der häufig niedrigen Taktfrequenzen stark beschränkt. Um auf den Cortex-M Prozessoren eine höhere Leistung für genannte Anwendungen zu erzielen, hat Arm die "Helium"-Erweiterung entwickelt und im Jahr 2019 zusammen mit der neuesten Version 8.1 des Arm M-Profils vorgestellt. Die Helium-Erweiterung ist eine Vektorerweiterung nach Vorbild der Neon-Erweiterung und teilt sich mit ihr einige Features und Prinzipien, wenn auch teilweise mit größeren Unterschieden, die v.a. in einem Konzept zur Überlappung von Instruktionen bestehen, welches elementar für optimale Leistung ist.

Während sich ein Großteil der Forschung dabei bisher auf die populären Architekturen wie x86-64 und Aarch64 sowie GPUs und eigenständige Hardwarebeschleuniger wie TPUs konzentriert hat, gibt es für die Helium-Erweiterung nach derzeitigen Stand nur eine Bibliothek zur Matrixmultiplikation, die Helium unterstützt. Ebenfalls gibt es keine Literatur, die sich mit der Optimierung von Matrixmultiplikation mittels der Helium-Erweiterung beschäftigt.

Daher werde ich in dieser Arbeit die Cortex-M Prozessorreihe mitsamt der Helium-Erweiterung beschreiben und ihre Performancecharakteristiken analysieren. Aus den gewonnenen Erkenntnissen wird ein JIT-Compiler zur effizienten Matrixmultiplikation entwickelt. Die entwickelte Lösung erreicht einen durchschnittlichen Geschwindigkeitszuwachs von 1,9x gegenüber der vorhandenen Referenzimplementierung von Arm und bis zu 99% der theoretisch erreichbaren Leistung des Cortex-M55.

Kapitel 2 beschreibt die Armv8.1-Architektur und die Helium-Erweiterung, welche als Grundlage für die Implementierung der Matrixmultiplikation genommen wird. In Kapitel 3 werden charakteristische Eigenschaften von Embedded Hardware betrachtet und das Alif Ensemble E7 als typischer Vertreter eines Embedded Systems vorgestellt. Kapitel 4 zeigt An- und Herausforderungen der Just-In-Time-Kompilierung auf Embedded Hardware, während in Kapitel 5 die Umsetzung der Matrixmultiplikation auf Embedded Hardware mithilfe der Helium-Erweiterung und eines Just-In-Time-Compilers beschrieben wird. Ka-

pitel 6 zeigt Ergebnisse der Implementierung und vergleicht die vorgestellte Lösung mit der Referenzimplementierung.

Die Helium-Erweiterung bietet weitaus mehr Instruktionen und Features als für Matrix-multiplikation benötigt wird; bei ihrer Beschreibung wird daher besonderer Wert auf die für Matrixmultiplikation benötigten Features gelegt und andere Neuerungen weggelassen.

Jeglicher genutzter Programmcode ist verfügbar unter https://github.com/01ill/e7-appkit-lab.

# 2. Embedded Hardware I: Arm M-Profil

Grundlage für die Implementierung der Matrixmultiplikation wird das Armv8.1-M-Profil sein, das etwa vom Cortex-M55 implementiert wird. Dies unterscheidet sich in einigen Punkten von dem bekannten Arm A-Profil, welches von den Prozessoren der Cortex-A-Reihe unterstützt wird. Aus diesem Grund werden im Folgenden die Grundlagen und Besonderheiten der Arm M-Profil-Architektur und des Cortex-M55 erklärt. Dabei werden zuerst die M-Profil-Prozessorreihe, die Eigenschaften des Cortex-M55 und die Unterschiede zum A-Profil beschrieben. Zum Schluss erfolgt eine detaillierte Charakterisierung des vom Armv8.1-M-Profil unterstützten Thumb2-Instruktionssatzes (T32) und insbesondere der Helium-Erweiterung. Dabei wird jeweils vor allem auf den Einfluss auf die Performance für Matrixmultiplikation eingegangen.

#### 2.1. Cortex M-Profil Prozessorreihe

Die von Arm entwickelten Prozessorarchitekturen werden von Arm grundsätzlich in drei Kategorien eingeteilt: Einerseits die Cortex-A Prozessoren, welche das A-Profil implementieren und auf die Ausführung von Betriebssystemen ausgerichtet sind und sich somit in zahlreichen Systemen von Smartphones bis Laptops finden. Cortex-R Prozessoren weisen größere Überschneidungen mit Cortex-A Prozessoren auf, sind aber für den Einsatz in Echtzeit-Systemen, wie Modems oder Festplattencontrollern, konzipiert. Zuletzt gibt es die Cortex-M-Prozessoren, welche auf die Bedürfnisse von eingebetteten Systemen zugeschnitten sind. Außerdem gibt es die Arm Neoverse Prozessoren für den Servereinsatz, welche ebenfalls das A-Profil implementieren.

Im Unterschied zu den A-Prozessoren haben die M-Prozessoren kein Speicherverwaltungssystem und können somit keine modernen Betriebssysteme ausführen. Der Fokus wird auf stark ressourcenbeschränkte Anwendungen in eingebetteten Systemen gelegt. Statt 64-Bit wird auf eine 32-Bit-Architektur gesetzt, da es nicht nötig ist, mehr Speicher zu adressieren. Außerdem wird nicht auf eine mehrstufige Cache-Architektur und großen DRAM gesetzt, sondern typischerweise auf eine zweigeteilte Speicherarchitektur (siehe 3.2) bestehend aus einem mit Tightly Coupled Memory (TCM) realisierten Echtzeitspeicher, aus dem Speicheranfragen im Normalfall innerhalb eines Zyklus abgearbeitet werden, sowie einem mit L1-Cache versehenen latenzbehafteten Speichersystem. TCM und L1-Cache sind nicht auf allen Modellen der M-Reihe verfügbar und sind vom CPU-Hersteller in der Größe konfigurierbar.

#### 2.1.1. Cortex-M55

Von Arm im Februar 2020 vorgestellt, war der Cortex-M55 der erste Prozessor, der auf dem Armv8.1-M Profil aufbaute und die Helium-Erweiterung unterstützte [42]. Somit war es auch das erste Modell, von dem kommerziell erhältliche Entwicklerboards wie das Alif

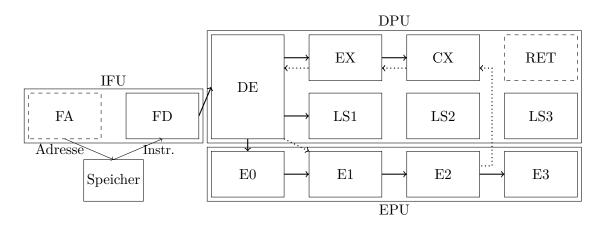

Abbildung 1: Pipeline des Cortex-M55. Grafik übernommen von [5]

E7 Ensemble erschienen, welches für die Umsetzung dieser Arbeit genutzt wurde. Kommerzielle Anwendung findet der Cortex-M55 u.a. in Smartwatches [31, 32] oder Kopfhörern [14].

Der Cortex-M55 siedelt sich mit seiner Leistungsfähigkeit in der Mitte der M-Profil-Prozessoren an, bietet mehr Leistung als M23 und M52, aber weniger Leistung als sein Nachfolger Cortex-M85 [11]. Der Grund für den Performanceunterschied liegt vor allem im Design der Pipeline. Daher erfolgt hier zuerst eine detaillierte Beschreibung der Pipeline gefolgt von einer Beschreibung der daraus implizierten Dual-Issue-Fähigkeiten sowie einer kurzen Beschreibung der typischen Speicherarchitektur.

**Pipeline** Beim Cortex-M55 wird zwischen den standardmäßigen skalaren Instruktionen sowie den Vektorinstruktionen der Helium-Erweiterung unterschieden. Für die Skalarinstruktionen wird eine vierstufige Pipeline genutzt, während für die Helium-Instruktionen eine fünfstufige Pipeline genutzt wird. Die Pipeline ist dabei komplett In-Order, das heißt, dass alle Instruktionen in der Reihenfolge ausgeführt werden, in der sie abgesetzt werden und keine automatische optimierte Anordnung der Instruktionen durch die CPU vorgenommen wird. Für die Entwicklung von performanten Algorithmen bedeutet dies, dass jede Instruktion optimal angeordnet werden muss, um die theoretisch erreichbare Performance zu erreichen.

Die Pipeline ist aus der Instruction Fetch Unit (IFU) sowie der Data Processing Unit (DPU) und Extension Processing Unit (EPU) zusammengesetzt. Dabei ist die EPU nur für die Floating-Point- (FP) und Helium-Instruktionen zuständig und ist nur vorhanden, wenn auch die FP- oder Helium-Erweiterung implementiert wird.

Von der aus "Fetch Adress"-Stufe<sup>2</sup> (FA) und "Fetch Data"-Stufe (FD) aufgebauten IFU werden die Instruktionen aus dem Speicher geladen. Dabei werden in jedem Zyklus 32 Bit geladen, d.h. entweder eine 32-Bit- oder zwei 16-Bit-Instruktionen. Instruktionen können entweder aus dem TCM oder dem Instruktions-Cache geladen werden. Zudem wird die Erkennung des Endes einer Low-Overhead-Schleife (siehe 2.2.3) von der FA übernommen. Von der FD werden die geladenen Instruktionen an die Decode-Stufe (DE) der DPU gegeben.

<sup>&</sup>lt;sup>1</sup>Vgl. Arm Ltd., Cortex-M55 Software Optimization Guide, S. 11ff. Ebenso wie die nachfolgende Beschreibung der Pipeline.

<sup>&</sup>lt;sup>2</sup>Die englischen Bezeichnungen der Pipeline werden im Folgenden so wiedergegeben, wie sie im Software Optimization Guide des Cortex-M55 stehen.

Von der DE werden die Instruktionen dekodiert und Operanden-Register gelesen. Außerdem enthält sie die Logik für strukturelle Gefahren, d.h. Instruktionen, bei denen es zu Lese-/Schreib-Konflikten kommen kann. Helium- und FP-Instruktionen werden an die Decode-Stufe der EPU weitergeleitet; alle anderen Instruktionen können direkt dekodiert und von dort entweder an die EX oder LS1 weitergegeben werden. Es existieren drei Register-Lese-Ports wovon einer für Dual-Issue-Fälle reserviert ist. Zudem können Daten aus der EX und CX an die DE weitergeleitet werden.

Skalare Instruktionen werden von der DE an die "Simple EXecute"-Stufe (EX) gegeben, wo ein Großteil der arithmetischen Integer-Instruktionen abgearbeitet werden. Daten können entweder aus der Register-Bank oder der CX gelesen werden. Können Instruktionen nicht komplett bearbeitet werden wie z.B. bei Integer-Multiplikation, werden sie an die CX weitergegeben. Ansonsten werden die Ergebnisse bereits hier zurück in die Register geschrieben.

In der "Complex eXecute"-Stufe (CX) werden Instruktionen abgearbeitet, die nicht von der EX abgearbeitet werden können. Zum Schreiben von Ergebnissen stehen hier zwei Schreib-Ports zur Verfügung, die z.B. bei Long-Multiply-Instruktionen aber auch beim Verschieben von Werten aus den Vektorregistern benötigt werden. Müssen Daten zurück in den Speicher geschrieben werden, werden sie mit den Daten aus EX kombiniert und an RET gegeben. Die "Retire"-Stufe (RET) gibt Daten aus dem Registerspeicher an den TCM oder Datencache.

Lade- und Speicherinstruktionen werden von der DE an die "Load-Store Address"-Stufe (LS1) gegeben. Dort wird zuerst ermittelt, an welche Speicherschnittstelle die Anfrage gegeben werden muss. Zudem werden hier unausgerichtete Zugriffe ausgerichtet, wobei währenddessen die Pipeline gestalled wird, weshalb immer auf die korrekte Ausrichtung von Daten im Speicher geachtet werden muss. In der "Load-Store Read Data"-Stufe (LS2) werden die Daten aus dem Cache bzw. TCM gelesen. Die Pipeline wird solange gestalled, bis die Daten verfügbar sind. Werden Daten geschrieben, kommt die "Load-Store Write Transfer"-Stufe (LS3) zum Einsatz, welche Daten an die entsprechenden Schnittstellen zum Speichern weitergibt.

Beim Ausführen von FP- oder Helium-Instruktionen wird die Instruktion von der DE direkt an die Decode-Stufe der EPU (E0) gegeben, wo sie dekodiert wird. Außerdem werden hier Probleme für die Überlagerung von Helium-Instruktionen ermittelt und wenn nötig die Pipeline gestalled.

Danach kommt die Instruktion in die "Operand Register Read"-Stufe (E1), wo die Operanden-Register aus dem Registerspeicher oder späteren Stufen gelesen werden. Skalare Register werden von der DPU übertragen. Nachdem die Instruktion dekodiert und Operanden gelesen wurden, wird die Instruktion in der "EPU Arithmetic"-Stufe (E2) abgearbeitet. Mit wenigen Ausnahmen werden hier Floating-Point-Instruktionen innerhalb von einem Zyklus und Helium-Instruktionen innerhalb von zwei Zyklen ausgeführt. Ausnahmen beinhalten v.a. Operationen auf FP64-Werten und Division. Zum Schluss kommt die Instruktion in die Writeback-Stufe (E3) wo die Ergebnisse in den Vektor-Registerspeicher geschrieben werden.

In der EPU existieren die vier Ausführungspipelines System-Register (SY), Load/Store (LS), Integer Vector (I) und Floating Point (F), von denen jede für verschiedene Instruktionsarten zuständig ist. Dies ermöglicht die Überlagung von Helium-Instruktionen, indem verschiedene Pfade zur Ausführung verschiedener Instruktionstypen bereitgestellt werden.

Aus diesem Pipeline-Design folgt, dass es zwar möglich ist, in jedem Zyklus eine Instruktion auszuführen, wenn die Bedingungen dafür gegeben sind, aber darauf geachtet werden muss, dass die Instruktionen optimal angeordnet sind und Daten entweder im TCM oder

im Cache vorhanden sein müssen sowie korrekt ausgerichtet, da sonst die gesamte Pipeline aufgehalten wird. $^3$

**Dual Issue** Der Cortex-M55 kann laut Arm entweder eine 32-Bit- oder in bestimmten Situationen auch zwei 16-Bit-Instruktionen zugleich ausführen, was von Arm als "Limited dual-issue of common 16-bit instruction pairs" bezeichnet wird.

Für Dual Issue stehen dafür zwei Slots zur Verfügung, wobei 16-Bit-Instruktionen in drei Kategorien eingeteilt werden: Entweder sie sind gar nicht dual-issue-fähig, können nur aus Slot 0 oder zuletzt aus beiden Slots ausgeführt werden.<sup>5</sup> Meist können Instruktionen mit Immediates aus beiden Slots und die jeweilige Variante mit Register-Parametern nur aus dem ersten Slot ausgeführt werden, da die DE-Stage der Pipeline nur drei Register-Read-Ports besitzt und es somit nicht möglich ist, vier Register in einem Zyklus zu lesen.

In Tests war es mir aber nicht möglich, einen Performancezuwachs bei dual-issued-Instruktionen auszumachen. Dazu wurden verschiedene Instruktionsanordnungen der MOV-Instruktion in Register- und Immediate-Variante getestet. Außerdem wurde getestet, ob eine 16-Bit-CMN-Instruktion ohne dual-issue-Fähigkeit die gleiche Leistung erbringt. Wie in Tabelle 1 zu sehen ist, ist die Variante mit den aus beiden Slots dual-issue-fähigen MOV-Instruktionen so schnell, wie die nicht dual-issue-fähige CMN-Instruktion. Es ist allerdings ebenso ein Vorteil gegenüber der Nutzung von 32-Bit-Instruktionen sichtbar.

| Test                                         | CPU-Zyklen |

|----------------------------------------------|------------|

| 2x 16-Bit-MOV<br>Dual Issue aus beiden Slots | 6492       |

| 2x 32-Bit-MOV                                | 8592       |

| 2x 16-Bit-CMN<br>Kein Dual Issue             | 6492       |

| 2x 32-Bit-CMN                                | 8592       |

Tabelle 1: Vergleich von Dual-Issue, 16-Bit- und 32-Bit-Instruktionen. Jeweils 200 Iterationen unterbrochen von zwei NOP-Instruktionen.

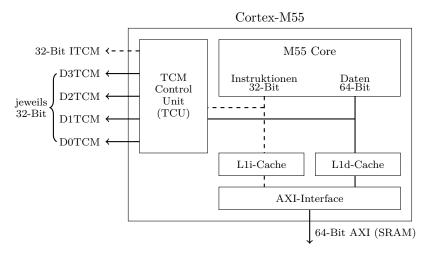

Speicherschnittstellen Der Cortex-M55 unterstützt wie auch die anderen Prozessoren des M-Profils verschiedenste Schnittstellen, um auf Speicher zurückgreifen. Als Hauptschnittstelle wird ein 64-Bit-AXI-Bus genutzt über den der Hauptspeicher angebunden ist. Es werden pro Zyklus ein Instruktionszugriff von 32 Bit sowie ein Datenzugriff von zweimal 32 Bit also 64 Bit unterstützt. Der AXI-Bus ist, wenn vorhanden, mit dem Instruktionsund Datencache verbunden. Außerdem kann optional ein Instruktions- und Daten-TCM genutzt werden, wobei der Instruktions-TCM wieder mit einem 32-Bit-Pfad und der Daten-TCM mit vier unabhängigen 32-Bit-Pfaden angebunden ist. Damit wird ermöglicht, dass in jedem Zyklus die unterstützten 64 Bit Daten und 32 Bit Instruktionen geladen werden können. Prinzipiell ist es erlaubt, Instruktionen in den Daten-TCM zu speichern und Daten in den Instruktions-TCM; durch die unterschiedliche Anzahl an Pfaden für Instruktions- und Daten in den Daten-TCM zu speichern (siehe 4.1).

Wie in Abbildung 2 zu sehen, ist dabei der TCM nah an der CPU angebunden und übergeht die Cache-Architektur völlig. Der über AXI angebundene Speicher verfügt über

<sup>&</sup>lt;sup>3</sup>Vgl. Arm Ltd., Cortex-M55 Technical Reference Manual, S. 186.

<sup>&</sup>lt;sup>4</sup>Arm Ltd., Cortex-M55 Technical Reference Manual, S. 32.

<sup>&</sup>lt;sup>5</sup>Vgl. Arm Ltd., Cortex-M55 Software Optimization Guide, S. 16.

Abbildung 2: Speicheranbindung des Cortex-M55.<sup>6</sup> Abbildung übernommen von [40].

einen L1-Cache für Daten und Instruktionen, so dass auch hier bei optimiertem Caching 64 Bit an Daten pro Zyklus geladen werden können. Wie bereits aus der Pipelinebeschreibung hervorging, wird hier nochmal deutlich, wie wichtig es ist, dass die performance-kritischen Daten entweder im TCM abgespeichert werden oder mittels Caching dafür gesorgt wird, dass ein Großteil der Daten immer im Cache vorhanden ist, da es sonst zu Pipeline-Stalls kommen kann.

#### 2.1.2. Weitere Prozessoren mit M-Profil

Neben dem Cortex-M55 existieren aktuell elf weitere Prozessoren der M-Familie im Angebot von Arm, wobei v.a. der Cortex-M85 als leistungsfähigerer Nachfolger des Cortex-M55 erwähnenswert ist. Im Gegensatz zum M55 ist hier ein Großteil der Instruktion dual-issuefähig. Außerdem wird eine längere sieben-stufige In-Order-Pipeline für skalare Instruktionen und eine neun-stufige Pipeline für Helium-Instruktionen genutzt [7]. Zugleich führt er ebenso wie der M55 pro Zyklus zwei Beats einer Helium-Instruktion aus. Auch die Speicherarchitektur ist beim Cortex-M85 auf die erweiterte Performance ausgelegt, indem statt einer 32-Bit-Schnittstelle für das Laden von Instruktionen auf eine 64-Bit-Schnittstelle für das Laden von zwei Instruktionen pro Zyklus gesetzt wird.

#### 2.2. Armv8.1-M-Profil

Im Februar 2019 von Arm angekündigt [18], ist das Armv8.1-M-Profil der Nachfolger des Armv8-M-Profils und bringt Änderungen wie die Helium-Erweiterung, Low-Overhead-Loops, Instruktionsmaskierung sowie Unterstützung für die Datentypen FP16 und INT8. Ansonsten ist Armv8.1-M rückwärts kompatibel zu Armv8-M.

Wie bereits seine Vorgänger stellt Armv8.1-M insgesamt 16 General-Purpose-Register (GP-Register) bereit, von denen drei für Link Register, Stack Pointer und Program Counter reserviert sind. Jedes dieser Register kann dabei 32 Bit speichern. Ebenso werden die Instruktionen des Thumb2-Instruktionssatz (T32) unterstützt.

Der T32-Instruktionssatz beinhaltet viele Instruktionen, die auch im A64-Instruktionssatz der Aarch64-Architektur vorhanden sind, wie Arithmetik-, Lade- und Speicher- sowie

<sup>&</sup>lt;sup>6</sup>Vgl. Arm Ltd., Cortex-M55 Technical Reference Manual, S. 29ff

Branchinginstruktionen. Besonderheit von T32 ist die Verfügbarkeit von bestimmten Instruktionen in 16-Bit- und 32-Bit-Enkodierung, wobei die 16-Bit-Enkodierungen meist starke Einschränkungen, wie kleine Offsets und eingeschränkte Registerauswahl besitzen. In Armv6-M werden dabei von T32 nur 56 Instruktionen implementiert, von denen ein Großteil nur in 16-Bit-Enkodierung unterstützt wird [41]. Armv7-M unterstützt eine deutlich größere Anzahl an Instruktionen und fügt für diese eine 32-Bit-Enkodierung hinzu. Außerdem können durch Implementierung von Erweiterungen weitere Instruktionen hinzugefügt werden. Für Armv7-M und aufwärts gibt es die DSP- und Floating-Point-Erweiterung (FP).

Von der DSP-Erweiterung werden Instruktionen bereitgestellt, die nach dem Single-Instruction-Multiple-Data-Prinzip (SIMD) arbeiten, d.h. mit einer Instruktion können mehrere Werte bearbeitet werden. Bei der DSP-Erweiterung wird dabei immer noch auf einem GP-Register gearbeitet. Die Instruktion UADD16 etwa teilt ein GP-Register in zwei Teile auf und rechnet dann separat auf jeder Hälfte. Wie später beschrieben, ist die Helium-Erweiterung eine deutlich mächtigere Erweiterung, um Instruktionen nach dem SIMD-Prinzip zu implementieren.

Die FP-Erweiterung stellt verschiedene Instruktionen bereit, um mit Fließkommazahlen zu rechnen. Im Unterschied zu Helium-Instruktionen werden dabei allerdings nur skalare Werte berechnet, auch wenn die Instruktionen teilweise die gleichen Namen besitzen. Außerdem bringt die FP-Erweiterung 32 FP-Register, welche später von der Helium-Erweiterung wiedergenutzt werden. In Armv8-M werden FP32 und FP64 unterstützt, in Armv8.1-M zusätzlich FP16.

Für Armv8-M gibt es außerdem die Main-Erweiterung, die implementiert werden muss, um rückwärtskompatibel mit Armv7-M zu sein. Wird die Main-Erweiterung nicht implementiert, besteht nur Kompatibilität mit Armv6-M und die DSP- und FP-Erweiterungen können nicht implementiert werden.

Im Folgenden werden die wichtigsten Neuerungen des Armv8.1-Profils beschrieben.

#### 2.2.1. Helium-Erweiterung

Da die bisherigen SIMD-Fähigkeiten der M-Reihe stark beschränkt waren, wird in Armv8.1-M die optionale M-Profile Vector Extension (MVE) eingeführt, die in Anlehnung an die bestehende Neon-Vektorerweiterung des A-Profils auch Helium-Erweiterung genannt wird. Dabei bestehen zwischen Neon und Helium sowohl einige Ähnlichkeiten, aber auch mehrere Unterschiede, so dass bei der Entwicklung von Algorithmen mit Helium bestehender Neon-Code meist nicht übernommen werden kann. Daher erfolgt hier zuerst ein Vergleich der Funktionalität von Helium- und Neon-Erweiterung gefolgt von einer Beschreibung der wichtigsten Konzepte der Helium-Erweiterung und deren Auswirkung auf die Performance. Zum Schluss werden einige Instruktionen vorgestellt, die für die Umsetzung von Matrixmultiplikation unerlässlich sind.

Sowohl Helium als auch Neon nutzen Vektorregister mit einer Länge von 128 Bit, die sich mit der Floating-Point-Einheit geteilt werden. Jedes Register wird in Lanes unterteilt, wovon jede ein Element beinhaltet, so dass bei einer Lanegröße von 32 Bit die Register in vier Lanes aufgeteilt werden und bei einer Instruktion vier Werte bearbeitet werden. Es werden Lanegrößen von 8, 16, 32 und 64 Bit unterstützt. Auch in der Semantik vieler Instruktionen bestehen Gemeinsamkeiten. So funktioniert beispielsweise das Addieren zweier Vektoren oder die gleichzeitige Multiplikation zweier Vektoren mit nachfolgender Addition auf einen Ergebnisvektor genau gleich, wenn auch mit unterschiedlicher Syntax. In den Instruktionen liegt der Unterschied vor allem darin, dass bei Helium keine Kombination von Vektoren mit einzelnen Lanes möglich ist, so dass keine Lane mit allen Elementen eines

Vektors addiert werden kann. Als Ersatz dafür stellt Helium bei vielen Instruktionen die Möglichkeit bereit, statt einer einzelnen Lane ein GP-Register anzugeben, welches dann als Lane interpretiert wird.

Anders als bei Neon stehen bei Helium statt 32 nur 8 Vektorregister zur Verfügung und es besteht nicht die Möglichkeit auf verschiedene Sichten zuzugreifen, so dass nur die 128-Bit-Q-Sicht unterstützt wird. Bei Helium besteht die Möglichkeit, Instruktionen zu maskieren (siehe 2.2.2), welche auf dem A-Profil erst mit der Scalable Vector Extension (SVE) eingeführt wurde [12]. Außerdem stehen Low-Overhead-Loops (siehe 2.2.3) und Tail-Predication (siehe 2.2.4) auf Neon nicht zur Verfügung.

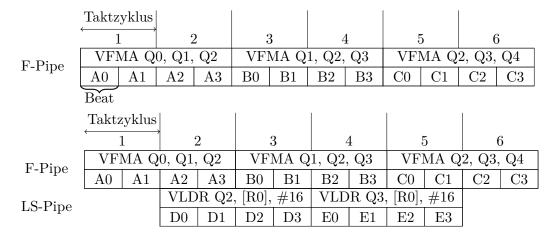

Der große Unterschied zu Neon besteht aber in der unterliegenden Architektur, die es ermöglichen soll, Vektorinstruktionen auf ressourcenbeschränkten Cortex-M-CPUs performant auszuführen. Das grundlegende Problem der Cortex-M-CPUs besteht darin, dass aufgrund von Platz- und Kostengründen die Speicher- und Rechenbandbreite nicht ausreicht, um 128 Bit in einem Zyklus zu laden bzw. zu bearbeiten. So hat etwa der Cortex-M55 eine interne Bandbreite von 64-Bit und unterstützt zwei 32-Bit Speicherzugriffe pro Zyklus, womit die Berechnung eines 128-Bit-Vektors zwei Zyklen benötigt und es zwangsläufig zum Stocken der Pipeline kommt. Auch der leistungsfähigere Cortex-M85 besitzt nur eine Bandbreite von 64 Bit während der Cortex-M52 nur eine Bandbreite von 32 Bit besitzt, wodurch die Abarbeitung eines Vektor ganze vier Zyklen benötigt. Um dieses Problem zu lösen, ermöglicht es Helium, Instruktionen zu überlagern und gleichzeitig auszuführen, so dass die vorhandene Bandbreite zu allen Zeiten ausgenutzt werden kann. Damit dies zuverlässig funktioniert, wird die Ausführung von Vektorinstruktionen in sogenannte "Beats" eingeteilt. Jeder Beat bearbeitet 32 Bit an Daten, so dass eine Instruktion in vier Beats unterteilt wird. Dabei ist es egal, welcher Datentyp ausgewählt, also auf wie vielen Lanes die Instruktion ausgeführt wird. Je nach Prozessor können dabei einer (Single-Beat), zwei (Dual-Beat) oder vier (Quad-Beat) Beats einer Instruktion pro Zyklus ausgeführt werden. Der Cortex-M52 mit seiner 32-Bit-Bandbreite ist dabei Vertreter der Single-Beat-Systeme während Cortex-M55 und M85 zwei Beats pro Zyklus abarbeiten. Die folgende Darstellung der Überlagerungsmöglichkeiten konzentriert sich daher auf Dual-Beat-Systeme.

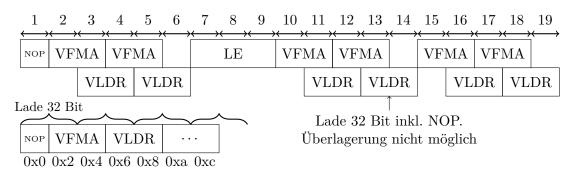

Im Cortex-M55 gibt es in der Vektorerweiterung je nach Instruktionstyp verschiedene Pfade (siehe 2.1.1), welche zeitgleich genutzt werden können. Dies erlaubt es, Instruktionen, welche unterschiedliche Pfade nutzen, gleichzeitig auszuführen.<sup>8</sup> Somit können in einem Zyklus insgesamt vier Beats und somit 128 Bit bearbeitet werden. Abbildung 3 zeigt, wie sich effektiv Lade-Instruktionen mit VFMA-Instruktionen überlagen lassen.

Bei Dual-Beat-Systemen werden beim Überlagern immer die letzten beiden Beats der ersten Instruktion<sup>9</sup> mit den ersten beiden Beats der zweiten Instruktion überlagert. Es ist nicht möglich, etwa die zweiten und dritten Beats zu überlagern. Dieses Design erlaubt es, auch Instruktionen gleichzeitig auszuführen, bei denen die erste Instruktion in ein Vektorregister schreibt und die zweite Instruktion aus diesem Register liest, da das Ergebnis der ersten beiden Beats bereits verfügbar ist, wenn die zweite Instruktion darauf zugreifen will. Im umgekehrten Falle - erst lesen, dann schreiben - gilt das gleiche: Wenn die zweite Instruktion schreibt, sind die Werte von der ersten Instruktion bereits gelesen, so dass es zu keinem Konflikt kommt.

Grundsätzlich lassen sich alle Vektorinstruktionen überlagen, wenn diese unterschiedliche Pfade in der Pipeline nutzen; aber auch Standard-Instruktionen können teilweise

<sup>&</sup>lt;sup>7</sup>Vgl. ARM V8M Referenz, B5.1, S. 178.

<sup>&</sup>lt;sup>8</sup>Im Cortex-M85 erlaubt der Einsatz von Instruktionsgruppen in der Pipeline sogar, etwa Lade- und Speicherinstruktionen zu überlagern.

<sup>&</sup>lt;sup>9</sup>Bei Single-Beat kann nur der letzte Beat überlagert werden

Abbildung 3: Überlappung von Instruktionen. VFMA nutzt Floating Point-Pipeline und VLDR die Load/Store-Pipeline. A0, A1, usw. bezeichnet die einzelnen Beats der Instruktionen.

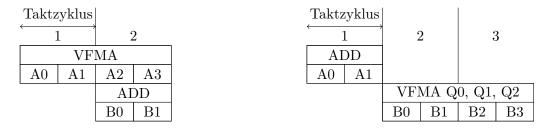

überlagert werden, auch wenn diese nicht mithilfe von Beats ausgeführt werden. Stattdessen können die letzten beiden Beats einer Vektorinstruktion mit der gesamten nachfolgenden Instruktion überlagert werden, wie in Abbildung 4 gezeigt. Nicht möglich ist es, eine Instruktion zu überlagern, wenn diese vor der Vektorinstruktion ausgeführt wird, da dies in den meisten Fällen einem Dual-Issue der Instruktionen gleichkommen würde, was vom Cortex-M55 nicht unterstützt wird. Hinzu kommen folgende Ausnahmen, in denen Instruktionen nicht überlagert werden können: (1) Arithmetische Skalarinstruktion steht hinter einer Lade- bzw. Speicher Vektorinstruktion mit Write-Back; (2) eine Skalarinstruktion steht hinter der letzten Instruktion in Low-Overhead-Loop und (3) wenn eine Abhängigkeit zwischen beiden Instruktionen besteht.

Abbildung 4: Überlappung von Vektor- mit Standard-Instruktionen.

Die Helium-Erweiterung erlaubt es somit, mit einem 64-Bit-Datenpfad pro Zyklus 128 Bit zu bearbeiten und pro Zyklus eine Instruktion auszuführen, selbst wenn die Helium-Instruktionen nur einen Durchsatz von einer halben Instruktion und eine Latenz von zwei Zyklen haben. Für die Entwicklung performanter Algorithmen bedeutet dies allerdings zusätzlichen Aufwand, da jede Instruktion optimal angeordnet werden muss, damit auch die gesamte Leistungsfähigkeit abgerufen werden kann. Außerdem muss die begrenzte Anzahl an Vektorregistern in Zusammenspiel mit der fehlenden Option, auf einzelne Lanes zuzugreifen, beachtet werden.

Für den Zweck dieser Arbeit folgt hier noch eine Beschreibung der wichtigsten Instruk-

<sup>&</sup>lt;sup>10</sup>Vgl. Arm Ltd., Cortex-M55 Software Optimization Guide, S. 46. Der Cortex-M85 hingegen erlaubt es durch seine Dual-Issue-Pipeline auch, bestimmte Instruktionen zu überlagern, wenn diese vor der Vektorinstruktion ausgeführt werden. Vgl. Arm Ltd., Cortex-M85 Software Optimization Guide, S. 43.

tionen, die für die Umsetzung effizienter Matrixmultiplikation mit FP32-Werten nötig sind.

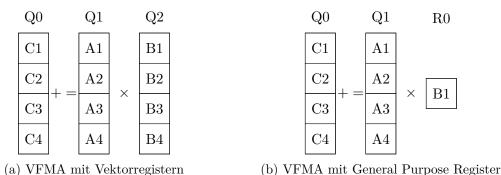

**VFMA** Die VFMA-Instruktion führt, wie in 5a gezeigt, eine Multiplikation auf den Elementen zweier Vektorregister durch und addiert die Ergebnisse auf die Elemente eines zusätzlichen Vektorregisters. Anders als bei Neon gibt es nicht die Möglichkeit, das erste Vektorregister mit einer einzelnen Lane des zweiten Vektorregisters zu multiplizieren. Dazu muss immer der Datentyp angegeben werden, sowie die drei benötigten Register:

VFMA.F32 Q0, Q1, Q2

Als Alternative wird von Arm angedacht, dafür ein GP-Register zu nutzen. In diesem Fall wird, wie in 5b gezeigt, jeder Wert im ersten Vektorregister mit dem Wert des GP-Registers multipliziert und die Ergebnisse auf die Werte des Vektor-Zielregisters addiert.

VFMA.F32 Q0, Q1, R0

Die VFMA-Instruktion unterstützt die Datentypen FP16 und FP32, wobei jeweils acht bzw. vier Elemente multipliziert und addiert werden.

Abbildung 5: VFMA-Varianten (jeweils FP32)

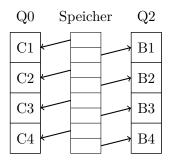

VLDRW und VSTRW Mit den VLDR- und VSTRW-Instruktionen werden Daten aus dem Speicher in Vektorregister geladen bzw. zurückgeschrieben. Grundsätzlich muss nur das Zielvektorregister, sowie das GP-Register welches die Speicheradresse hält, angegeben werden. Die VLDR-Instruktion lädt dann 128 Bit von der angegebenen Adresse. Wie bei Neon besteht dabei auch die Möglichkeit, mittels eines Immediates den Abstand zur Speicheradresse anzugeben, wobei der Abstand vor bzw. nach dem Laden angewandt und ebenfalls zurückgeschrieben werden kann. Anders als bei der LDR-Instruktion besteht aber nicht die Möglichkeit, ein GP-Register anzugeben, welches den Abstand angibt; einzige Alternative ist die Angabe eines Vektorregisters, welches den Abstand für jedes Element angibt.

Es ist nur möglich, einen Abstand von 512 Bytes (auf vier Bytes ausgerichtet) anzugeben, was bei FP32 bedeutet, dass nur 127 Elemente übersprungen werden können. Für Anwendungsfälle mit größeren Matrizen bedeutet dies, dass zwangsläufig Skalarinstruktionen zum Modifizieren der Zeiger mit Vektorinstruktionen vermischt werden müssen, wenn der Abstand zu den nächsten Werten im Speicher zu groß ist, um diesen mit einem Immediate abzubilden.

Anders als bei NEON ist es nicht möglich, mehr als 128 Bit mit einer Instruktion gleichzeitig zu laden, einzig die Instruktionen VLD2/VST2 und VLD4/VST4 existieren, welche allerdings 128 Bit auf zwei bzw. vier Vektorregister verteilen, wie in Abbildung 6

für VLD2 gezeigt. Dies würde sonst mit dem beschriebenen Beat-Konzept zwangsläufig zu Stalls in der Pipeline führen, da die Lade-Instruktionen mit anderen Instruktionstypen überlagert werden müssen.

Abbildung 6: Funktionsweise der VLD2-Instruktion

#### 2.2.2. Maskierung

Wenn es überschüssige Elemente gibt, diese aber ein Vektorregister nicht komplett füllen, müssen die verbleibenden Elemente maskiert werden, so dass keine Elemente aus dem Speicher geladen oder gespeichert werden, da dies zu unzulässigen Speicherzugriffen führen kann. Damit diese verbliebenen Elemente nicht mit skalaren Code bearbeitet werden müssen, stellt die Helium-Erweiterung die Möglichkeit bereit, Vektorinstruktionen zu maskieren, damit nur bestimmte Lanes bearbeitet werden. Dafür wird das Maskierungsregister VPR hinzugefügt, in dem gespeichert wird, wie viele Instruktionen und welche Lanes maskiert werden. Der Wert P0 im Register bestimmt, welche Lanes maskiert werden und die Werte MASK23 und MASK01 bestimmen, wie viele Instruktionen maskiert werden. <sup>11</sup> In jeder Vektorinstruktion wird geprüft, ob die Instruktion maskiert werden muss, indem das VPR-Register ausgelesen wird. Außerdem werden die MASK-Werte nach jeder Instruktion zurückgeschrieben, so dass nicht unendlich viele Instruktionen maskiert werden.

Abbildung 7: Maskierung einer VFMA-Instruktion. Lanes 1 bis 3 werden berechnet, während Lane 4 ignoriert wird

Mit der Instruktion VCTP wird angegeben, wie viele Lanes maskiert werden sollen, indem der Wert P0 gesetzt wird. Diese Instruktion muss nur einmal ausgeführt werden, da die Einstellung danach nicht zurückgesetzt wird. Außerdem muss die Instruktion VPST ausgeführt werden, mit der gesetzt wird, wieviele der folgenden Instruktionen maskiert werden. Abbildung 7 zeigt folgendes Beispiel einer einzelnen maskierten VFMA-Instruktion:

<sup>&</sup>lt;sup>11</sup>Vgl. Arm Ltd., Armv8-M Reference Manual, S. 186f, 1900.

```

mov r0, #3

vctp.32 r0

vpst

vfmat.f32 q0, q1, q2

```

Da die kleinste Lanegröße 8 Bit beträgt, werden bei Angabe von 32-Bit-Lanes für jede Lane insgesamt vier Werte in P0 gesetzt.

#### 2.2.3. Low Overhead Loops

Um Schleifen in Assembly umzusetzen, wird typischerweise eine Kombination aus Vergleichs-und Branch-Instruktionen genutzt. Dabei kann es zu einer Leerung der Pipeline und einem damit verbundenen Stocken der Programmausführung kommen, wenn einem Branch gefolgt wird, der nicht dem Standard-Programmfluss folgt, da an einen neuen Ort gesprungen wird, von dem noch keine Instruktionen geladen sind. Auf modernen CPUs wie der Cortex-A-Reihe sind dafür komplexe Branchvorhersageeinheiten verbaut, die ermitteln, welchem Branch gefolgt wird und von dort bereits die Pipeline füllen, womit der zusätzliche Aufwand minimiert wird. Aufgrund von Kosten- und Platzgründen sind aber nicht auf allen Cortex-M-CPUs Branchvorhersageeinheiten verbaut, weshalb durch Schleifen ein erheblicher Mehraufwand entstehen kann. Aus diesem Grund [21] wurden die sogenannten Low-Overhead-Loops bzw. Low-Overhead-Branches (LOB) als optimierte Alternative zu traditionellen Schleifenstrukturen zu Armv8.1-M hinzugefügt. 12

Grundidee der Low-Overhead-Loops ist es, mittels einem einzelnen zusätzlichen Register und wenigen zusätzlichen Instruktionen Schleifenstrukturen bereitzustellen, die auch ohne Branchvorhersage ohne zusätzlichen Mehraufwand ausgeführt werden.

**Umsetzung** Wie erwähnt, wird nur ein einzelnes zusätzliches 67-bit-Register<sup>13</sup> zum Speichern des Loop-Caches benötigt. Der Loop-Cache besteht dabei aus Start- und Endadresse der jeweiligen Schleife sowie aus Flags um zu speichern, ob man eine unendliche Schleife eingerichtet hat bzw. ob der Loop-Cache noch gültig ist.<sup>14</sup> Der Loop-Zähler wird nicht im Cache gespeichert, sondern im Link Register.

In der ersten Iteration der Schleife wird dieser Cache sowie das Link Register mittels einer Instruktion zum Beenden und einer zum Starten der Schleife befüllt. In den folgenden Iterationen wird in der Fetch-Stufe der Pipeline geprüft, ob die Programmadresse mit der Endadresse im Loop-Cache übereinstimmt, wobei die Instruktion zum Beenden des Loops nicht mehr ausgeführt wird. Wenn dies der Fall ist, wird wieder an die Startadresse des Loops gesprungen, insofern der Zähler im Link Register noch nicht auf Null dekrementiert wurde.

Somit fällt einerseits ein Großteil des Branching-Mehraufwands weg; zusätzlich erlaubt diese Architektur bei Implementierung der Helium-Erweiterung eine Überlagerung der letzten und ersten Instruktion der Schleife, was bei passenden Instruktionen zu einem weiteren Performancegewinn führt (siehe 2.2.1).

Anwendung Es werden drei zusätzliche Instruktionen eingeführt: WLS (While Loop Start) und DLS (Do Loop Start) starten eine Schleife und kopieren die Anzahl der Iterationen (per Register angegeben) in das Link Register. WLS bietet dabei zusätzlich die Möglichkeit, direkt zum Ende der Schleife zu springen, wenn keine Iterationen ausgeführt

<sup>&</sup>lt;sup>12</sup>Vgl. J. Marsh, Arm Helium Technology Reference Book, S. 32.

$<sup>^{13}\</sup>mathrm{Vgl.}$  Arm Ltd., Armv<br/>8-M Reference Manual, D1.2.163, S. 1735.

<sup>&</sup>lt;sup>14</sup>Vgl. Arm Ltd., Armv8-M Reference Manual, B3.28, S. 135f.

werden müssen. LE (Loop End) beendet eine Schleife und befüllt den Loop-Cache in der ersten Iteration, wobei die Startinstruktion des Loops angegeben werden muss, sowie das Link Register, um dieses in jeder Iteration zu dekrementieren.

Um zu prüfen, welchen Performancevorteil die Low-Overhead-Loops bieten, wurden verschiedene Schleifen-Varianten getestet, die in Abbildung 8 dargestellt sind. Einerseits eine Schleife mittels Backwards-Branch, bei dem sich die Branch- und CMP-Instruktionen am Ende der Schleife befinden und in jeder neuen Iteration an den Start der Schleife gesprungen wird. Zudem zwei Varianten von Forward-Branch, bei dem sich zusätzliche Branch-Instruktionen am Start der Schleife befinden und nach der letzten Iteration an das Ende der Schleife gesprungen wird, während in jeder Iteration bedingungslos an den Start gesprungen wird. Eine Variante davon nutzt die die CBZ-Instruktion, welche die CMP- und Branch-Instruktion kombiniert. Zuletzt wird eine einfache Schleife mit Low-Overhead-Loops getestet.

| mov r1, #0 mov r1, #0      |                          | dls lr, r0                | cbzStart:                 |  |  |

|----------------------------|--------------------------|---------------------------|---------------------------|--|--|

| loopStartB1:               | loopStartB2:             |                           | <pre>cbz r0, cbzEnd</pre> |  |  |

| vfma.f32                   | cmp r1, r0               | loopLOB:                  |                           |  |  |

| vfma.f32                   | bge b2End                | vfma.f32                  | vfma.f32                  |  |  |

| add r1, #1                 | vfma.f32                 | vfma.f32                  | vfma.f32                  |  |  |

| vfma.f32                   | vfma.f32                 | vfma.f32                  | subs r0, #1               |  |  |

| cmp r1, r0                 | add r1, #1               | vfma.f32                  | vfma.f32                  |  |  |

| vfma.f32                   | vfma.f32                 |                           | vfma.f32                  |  |  |

|                            | vfma.f32                 | <pre>le lr, loopLOB</pre> | <pre>b cbzStart</pre>     |  |  |

| <pre>blt loopStartB1</pre> | <pre>b loopStartB2</pre> |                           |                           |  |  |

|                            | _                        |                           |                           |  |  |

Abbildung 8: Micro-Benchmark von Branch-Backward, Branch-Forward, Low-Overhead Loop und CBZ-Branch

Wie in Tabelle 2 zu sehen, sind Schleifen mittels Low-Overhead-Loops schneller, selbst wenn wie beim Cortex-M55 eine einfache Branchvorhersageeinheit verbaut ist. Gegenüber dem optimierten Backward-Branch ist der Low-Overhead-Loop um 12% schneller. Hingegen sind Forward-Branch und der modifizierte Forward-Branch mit CBZ-Instruktion etwa 11% langsamer als der Backward-Branch, da beim Cortex-M55 bei Backwards-Branch die Latenz nach der ersten Iteration Null ist. Ein weiterer Vorteil des Low-Overhead-Loops ist die Einsparung eines zusätzlichen Registers, welches zum Speichern der Loop-Variable bei den anderen Methoden benötigt wird. Außerdem fällt der Programmieraufwand zum Prüfen der Schleifenbedingung weg, was die Implementierung einer Schleife einfacher gestaltet.

| Test                | Zeit abs. (ms) | Zeit rel. | Speedup |

|---------------------|----------------|-----------|---------|

| Backwards-Branch    | 2241           | 1.0       | 1.0     |

| Forward-Branch      | 2489           | 1.11      | 0.9     |

| Low Overhead Branch | 1992           | 0.89      | 1.12    |

| Forward-Branch CBZ  | 2489           | 1.11      | 0.9     |

Tabelle 2: Ergebnisse der verschiedenen Schleifen. Jede Variante wurde optimiert, so dass Instruktionen sich überlagern.

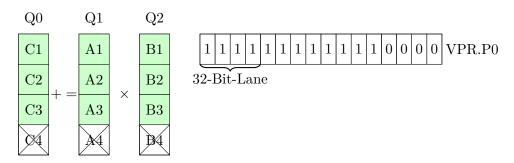

Grundsätzlich müssen sowohl 16- als auch 32-Bit-Instruktionen auf 2 Byte ausgerichtet werden. Für Helium-Instruktionen im Low-Overhead-Loop ist es zudem wichtig, dass

<sup>&</sup>lt;sup>15</sup>Vgl. Arm Ltd., Cortex-M55 Software Optimization Guide, S. 17f

sie auf 4 Byte ausgerichtet werden, da es sonst pro Iteration zu einer Verzögerung von einem Zyklus kommen kann [43]. Dies liegt daran, dass von der IFU (siehe 2.1.1) der Pipeline in jedem Zyklus 32 Bit geladen werden. Wie Abbildung 9 zeigt, kann bei fehlender Ausrichtung der ersten VFMA-Instruktion die letzte VLDR-Instruktion nicht mit der VFMA-Instruktion überlagert werden, da insgesamt zwei Zyklen zum Laden der kompletten VFMA-Instruktion benötigt werden. Von der IFU wird das Schleifenende erkannt und die erste Instruktion am Schleifenanfang geladen. Der TCM führt aber jeglichen Lese- und Schreibzugriff immer auf 4 Byte ausgerichtet aus. <sup>16</sup> Somit wird nicht die gesamte erste 32-Bit-Instruktion geladen, sondern die letzten 16 Bit vor der Schleife und die ersten 16 Bit der ersten Instruktion. Um die Instruktion auszuführen, ist nun ein weiterer Zyklus nötig.

Abbildung 9: Darstellung Problematik Code-Alignment. Start des Loops ist die erste VFMA-Instruktion. NOP ist 16-Bit Variante.

Dies stellt nur ein Problem dar, wenn sich letzte und erste Instruktion überlagern können, da sonst durch den Ressourcenkonflikt auch ein Stall entstehen würde, der die zusätzliche Ladezeit überdeckt. Auch in der normalen Programmausführung stellt das kein Problem dar, da man höchstens bei der ersten Helium-Instruktion eine Instruktion länger warten muss, da dies aber in Low-Overhead-Loops in jeder Iteration auftritt, muss hier besonders drauf geachtet werden. Tabelle 3 zeigt, dass bei einer Schleife mit 10000 Iterationen auch knapp unter 10000 mehr Zyklen benötigt werden, wenn sich die Instruktionen überlagern können. Wenn hingegen nur VFMA-Instruktionen ausgeführt werden, hat die Ausrichtung der Instruktionen keinen Einfluss auf die Laufzeit, da sich das Stocken der Pipeline mit dem Nachladen der Instruktion überlagert.

| Test                    | Zeit (µs) | Zyklen |

|-------------------------|-----------|--------|

| Helium Aligned          | 100       | 40245  |

| Helium Non-Aligned      | 125       | 50179  |

| Helium Aligned VFMA     | 200       | 80174  |

| Helium Non-Aligned VFMA | 200       | 80018  |

Tabelle 3: Test von ausgerichteten und nicht ausgerichteten Funktionen mit 10000 Iterationen einer Schleife.

Prinzipiell sollte also mindestens die erste Instruktion des Loops auf 4-Byte ausgerichtet werden. Dies kann etwa durch Einfügen einer zusätzlichen 16-Bit-NOP-Instruktion außerhalb der Schleife passieren. Bei handgeschriebenen Assembly-Code besteht dafür die Direktive .p2align, die den Programmcode ausrichtet.

<sup>&</sup>lt;sup>16</sup>Vgl. Arm Ltd., Cortex-M55 Technical Reference Manual, Table C-7, S. 369.

#### 2.2.4. Tail-Predication

Beim Umwandeln von skalaren in vektorisierten Code muss immer berücksichtigt werden, dass die Anzahl der zu bearbeitenden Elemente häufig kein Vielfaches der Werte im Vektorregister ist. Dies führt dazu, dass man die übrigen Elemente entweder mit skalaren Instruktionen oder maskierten Vektorinstruktionen abarbeiten muss. Um dies zu vermeiden, wird in Armv8.1-M die sogenannte Tail-Predication eingeführt, welche die bereits beschriebenen Low-Overhead-Loops erweitert. Dabei speichert das Link Register nicht mehr die Anzahl an Iterationen sondern die Anzahl an zu bearbeitenden Elemente, wobei in jeder Iteration die Anzahl der bearbeiteten Elemente abgezogen wird. <sup>17</sup> In der letzten Iteration werden dann zusätzlich alle Vektorinstruktionen automatisch maskiert, so dass sie die übriggebliebenen Elemente bearbeiten.

Damit dies genutzt werden kann, werden die Instruktionen WLSTP, DLSTP und LETP eingeführt, die Äquivalente zu den Low-Overhead-Loop-Instruktionen sind. Dabei wird bei WLSTP und DLSTP nun zusätzlich angegeben und bei Ausführung gespeichert, welche Größe die Vektor-Elemente besitzen. Die Datentypgröße entscheidet, wie viele Elemente in jeder Iteration bearbeitet werden. Zum Schluss der Schleife muss statt LE nun LETP ausgeführt werden. Nach jeder Iteration wird die Anzahl der bearbeiteten Elemente vom Link Register abgezogen.

In Listing 10 ist beispielhaft gezeigt, wie durch Einsatz von Tail-Predication vektorisierter Code zum Addieren zweier Vektoren deutlich vereinfacht werden kann. Es wird eine Größe von 32 Bit angegeben, da als Datentyp FP32 genutzt wird. Somit werden durch die VADD-Instruktion in jeder Instruktion vier Elemente addiert. Ist die Anzahl der Elemente nicht durch vier teilbar, werden die Instruktionen in der letzten Iteration maskiert und nur die benötigten Elemente geladen und gespeichert.

```

dls lr, r0 // r0 = vec_len / 4

dlstp.32 lr, r0 // r0 = vec_len

1Start:

1Start:

vldrw q1, [r1], #16

vldrw q1, [r1], #16

vldrw q2, [r2], #16

vldrw q2, [r2], #16

vadd.f32 q0, q1, q2

vadd.f32 q0, q1, q2

le lr, lStart

vstrw q0, [r3], #16

lEnd:

letp lr, lStart

// vec_len % 4 übrig

lEnd:

vctp // maskieren

vpst

vldrwt q1, [r1], #16

vldrwt q2, [r2], #16

vaddt.f32 q0, q1, q2

vstrwt q0, [r3], #16

```

Abbildung 10: Vergleich von Standard-Schleife und Tail-Predication bei Vektor-Addition

## 2.3. Arm Microcontroller Software-Stack

Um die Entwicklung von Embedded Software für Entwickler zu vereinfachen, stellt Arm unter dem Namen "Cortex Microcontroller Software Interface Standard" (CMSIS) verschiedene Softwarebibliotheken und Anwendungen bereit [10]. Für diese Arbeit sind dabei insbesondere die Tools zur Kompilation erwähnenswert.

$<sup>^{17}\</sup>mathrm{Vgl.}$  J. Yiu, Blending DSP and ML features into a low-power general-purpose processor, S. 9.

CMSIS ist dabei grundlegend eine Schnittstelle für Hardware- und Software-Entwickler um eine Abstraktionsebene für die Hardware bereitzustellen, so dass etwa Treiber und Software schneller entwickelt werden können. Es werden die Bibliotheken CMSIS-NN [27] und CMSIS-DSP bereitgestellt, um ML- und DSP-Kernel auszuführen.

Über YAML-Dateien können Projekte konfiguriert werden, um diese dann mit verschiedenen Toolchains zu kompilieren. Von Arm wird eine eigene Version von clang bereitgestellt, sowie eine gcc-Version mit Unterstützung für das M-Profil, wobei die Unterstützung für Helium in armclang besser ausgebaut ist. Etwa Tail Predication wurde erst in der neuesten GCC15-Version hinzugefügt [17], die aber in CMSIS noch nicht verfügbar ist. Aufgrund der besseren Performance wird in dieser Arbeit immer armclang genutzt, was von Arm bei der DSP-Bibliothek auch explizit empfohlen wird.

Außerdem werden von Arm sogenannte Intrinsics bereitgestellt, d.h. Funktionen, mit denen direkt im C-Code Platzhalter eingefügt werden können, die dann beim Kompilierungsprozess zu den angegebenen Instruktionen kompiliert werden.

### 3. Embedded Hardware II: Alif E7 Board

Neben den bereits erwähnten kommerziellen Umsetzungen existieren es auch mehrere Implementierungen des Cortex-M55 in Entwicklerboards. Eine der ersten Umsetzungen waren die "Ensemble"-Entwicklerboards von Alif Semiconductors, die diese 2023 veröffentlichten [33]. Zu diesen gehört auch das Ensemble E7-Board, welches in dieser Arbeit genutzt wird. Das Ensemble E7 bietet eine typische Implementierung eines Cortex-M Prozessors mit L1-Cache und zwei Speicherbereichen bestehend aus SRAM und TCM. Es werden zwei Cortex-M55, die sich v.a. in der Taktfrequenz unterscheiden, verbaut. Auf beiden ist die Helium-Erweiterung mit Integer- und Floating-Point-Unterstützung verbaut.

Von Alif wird eine Integration in das CMSIS-Framework bereitgestellt, wodurch der benötigte Code zum Booten geladen werden kann. Außerdem werden automatisch Cache und Features wie Low-Overhead-Branches aktiviert. Zum Ausführen von Tests wird ein Timer mit 32768 Hz bereitgestellt.

Abschnitt 3.1 beschreibt das Rechensystem des Ensemble E7 mit seinen in zwei verschiedenen Bereichen verbauten Kernen während 3.2 die verbauten Speicherbereiche und deren Performance beschreibt.

#### 3.1. Rechenleistung

Auf dem Ensemble E7 sind ein sogenannter High-Efficiency- (HE) und ein High-Performance-Bereich (HP) verbaut, sowie ein Application-Subsystem (APSS). Die HE und HP-Bereiche nutzen dabei jeweils eine Cortex-M55 CPU, welche im HP-Bereich mit 400 MHz und im HE-Bereich mit 160 MHz taktet. Im Application-Bereich kommt eine Cortex A32-CPU in Dual-Core Konfiguration zum Einsatz. Da für die Implementierung der Matrix-multiplikation mit der Helium-Erweiterung der Anwendungsbereich nicht nötig ist, wird die Beschreibung dieses Bereiches hier ausgespart.

Der Cortex-M55 Kern in HP- und HE-Bereich ist mit Helium-Erweiterung und Unterstützung für Integer- und Fließkomma-Operationen ausgestattet. Jeder Kern hat 32 KB an Daten- und Instruktionscache. An beiden Kernen ist jeweils ein Daten-TCM und ein Instruktions-TCM angebunden. Die Bereiche unterscheiden sich v.a. in der Taktung der CPU. So taktet der HP-Bereich mit 400 MHz während der HE-Bereich mit 160 MHz taktet. Außerdem ist der TCM-Speicher des HP-Bereiches größer und umfasst 256 KB für den Instruktions- und 1024 KB für den Daten-TCM. Der TCM-Speicher des HE-Bereich

| Test        | GFLOPS |

|-------------|--------|

| Scalar FP32 | 0.752  |

| Scalar FP64 | 0.033  |

| Helium FP32 | 1.599  |

| Test        | GFLOPS |

|-------------|--------|

| Scalar FP32 | 0.301  |

| Scalar FP64 | 0.013  |

| Helium FP32 | 0.639  |

Tabelle 4: Peak Performance HP-Core Tabelle 5: Peak Performance HE-Core

umfasst nur jeweils 256 KB für Instruktions- und Daten-TCM (siehe 3.2). 18

Da der Cortex-M55 ein Dual-Beat-System ist, benötigt er zwei Zyklen, um eine Vektorinstruktion, die auf einem 128-Bit-Vektorregister arbeitet, auszuführen. Eine einzelne VFMA-Instruktion mit Datentyp FP32 führt auf vier Elementen jeweils eine Multiplikation und eine Addition durch, d.h. insgesamt acht Fließkomma-Operationen (FLOP). Die theoretische maximale Leistung ergibt sich also folgendermaßen für HP- und HE-Bereich:

8 FLOP \* 400 MHz \*

$$\frac{1}{2}$$

= 1600 MFLOPS = 1.6 GFLOPS (HP)

8 FLOP \* 400 MHz \*

$$\frac{1}{2}$$

= 1600 MFLOPS = 1.6 GFLOPS (HP)

8 FLOP \* 160 MHz \*  $\frac{1}{2}$  = 640 MFLOPS = 0.64 GFLOPS (HE)

Durch einen Microbenchmark von aneinandergereihten VFMA-Instruktionen kann die theoretisch erreichbare Leistung auch praktisch erreicht werden. Dabei ist es unerheblich, ob zwischen den einzelnen Instruktionen Abhängigkeiten bestehen; die Leistung bleibt gleich. Außerdem wird getestet, inwiefern die theoretisch erreichbare Leistung erhalten bleibt, wenn die VFMA-Instruktionen mit VLDR-Instruktionen vermischt werden. Auch hier bleibt die Performance erhalten, insofern die Daten im TCM liegen, weil VLDR und VFMA verschiedene Pipelines nutzen und sich so überlagern können, während bei einer Aneinanderreihung von VFMA-Instruktionen nur die FP-Pipeline genutzt würde und sich keine Instruktionen überlagern.

Wie in Tabelle 4 zu sehen ist, wird die Peak Performance annähernd erreicht. Im Vergleich zur skalaren Variante der früheren Floating-Point-Erweiterung ist ein zweifacher Speedup zu beobachten. Zudem ist zu sehen, dass die FP- und Helium-Erweiterung nicht auf das schnelle Rechnen mit doppelter Präzision ausgelegt sind, da FP64 nicht von Helium unterstützt wird und bei der FP-Erweiterung nur einen Durchsatz von  $\frac{1}{23}$  hat.

Das gleiche Verhalten ist bei Ausführung auf dem HE-Kern zu sehen, wo ebenfalls die jeweilige Peak-Performance erreicht wird.

#### 3.2. Speichersystem

Wie bereits im Abschnitt über die M-Profil-Prozessoren beschrieben, wird grundsätzlich auf zwei verschiedene Speichersysteme gesetzt: Den schnellen, direkt an die CPU angebundenen TCM-Speicher, sowie den langsameren, latenzbehafteten Hauptspeicher, der Caches nutzen kann. Auch auf dem Ensemble E7 hat man eine solche Speicherstruktur. Außerdem ist ein nichtflüchtiger MRAM-Speicher zum dauerhaften Speichern des Programmcodes vorhanden.

Insgesamt stehen 13.5 MB Speicher zur Verfügung, wovon 5.5 MB für den MRAM zur Verfügung stehen. Der SRAM-Bereich ist in einzelne Teile zerlegt, von denen einige für den TCM zur Verfügung stehen.

Mittels Linker-Skript werden die einzelnen Speicherbereiche konfiguriert. Standardmäßig werden alle Variablen im Daten-TCM abgelegt, sowie alle Instruktionen beim Bootprozess in den Instruktions-TCM kopiert. Es sind 8 KB Heap und 16 KB Stack vorkonfiguriert.

<sup>&</sup>lt;sup>18</sup>Vgl. Alif Semiconductors, Datasheet Ensemble Family E7 Series v2.11, S. 12ff.

Der geringe dynamische Speicher und die verschiedenen Speichersegmente bedeuten, dass es sehr schnell zu Problemen kommen kann, wenn dynamische Speicherverwaltung genutzt wird. Um den Speicherort und damit das Speichersegment zu kontrollieren, werden Größe und Ort von Arrays hier immer bereits vor der Kompilierung festgelegt.

Über die Memory Protection Unit (MPU) kann der Cache konfiguriert werden. Standardmäßig werden beim SRAM0 Lesezugriffe gecached und Schreibzugriffe immer direkt zurückgeschrieben, so dass der Cache umgangen wird.

# 3.2.1. Dauerhafter Speicher - MRAM

Der MRAM auf dem Ensemble E7 umfasst 5.5 MB auf dem alle Daten untergebracht werden müssen, die auch nach Stromverlust noch vorhanden sein sollen. Dies umfasst in erster Linie den Programmcode. Um den Programmcode schnell auszuführen, wird er mittels Linkerskript beim Boot in den Instruktions-TCM kopiert. Der MRAM ist über den AXI Bus mit 64 Bit angebunden, taktet mit 33 MHz und gehört zur HP-Region. <sup>19</sup> Laut Alif sind Schreibraten von 2.28 MB/s und Leseraten von 232 MB/s erreichbar. <sup>20</sup> Da der Programmcode nachfolgend immer auf den TCM kopiert wird und der MRAM somit, außer zum nichtvolatilen Speichern unwichtig ist, werden diese Angaben hier nicht überprüft und der MRAM im Folgenden ignoriert.

#### 3.2.2. Langsamer Speicher - SRAM

Der SRAM ist auf dem Ensemble E7 als Hauptspeicher gedacht und in mehrere Teile unterteilt, die verschiedene Zwecke und Taktraten haben und auch unterschiedlich angebunden sind. Insgesamt sind 13.5 MB SRAM verfügbar. Es sind SRAM-Teile 0 bis 9 verfügbar, wobei SRAM2 bis SRAM5 als TCM-Speicher angebunden sind (siehe 3.2.3). SRAM0 und SRAM1 sind am HP-Bereich über einen 64-Bit-AXI-Bus mit 400 MHz angebunden, während SRAM6 bis SRAM9 am HE-Bereich angebunden sind. SRAM0 und SRAM1 haben eine Kapazität von 4 MB bzw. 2.5 MB und sollen als gemeinsamer Hauptspeicher für Anwendungen dienen. Die anderen SRAM-Bereiche sind für nicht performance-kritische Anwendungen gedacht, werden aber hier nicht weiter betrachtet. Aufgrund der vergleichsweise großen Kapazität wird für die folgenden Tests immer der SRAM0-Bereich genutzt.

Alif zufolge sind Leseraten von 1350 MB/s (558 MB/s im HE-Bereich) auf SRAM0 möglich. Schreibraten werden mit 1824 MB/s (731 MB/s) angegeben. Außerdem werden bei SRAM0 die Daten- und Instruktionscaches genutzt, so dass bei Wiedernutzung von Daten die Lese- und Schreibraten erheblich höher sein können. Der verbaute Cortex-M55 unterstützt zwei 32-Bit-Zugriffe pro Zyklus, so dass eine maximale Bandbreite von 3.2 GB/s (1,28 GB/s) erreicht werden kann.

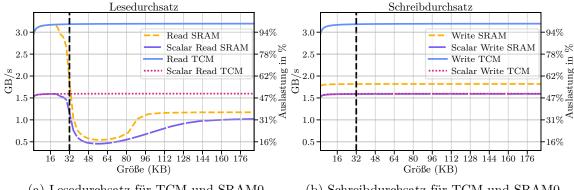

Um zu prüfen, welcher Durchsatz praktisch zu erreichen ist, wurden mittels Low-Overhead-Loop mehrere Lade- bzw. Schreibinstruktionen hintereinandergehangen, um ein Array aus FP32-Werten mehrfach zu laden und zusätzlich der Unterschied zwischen Vektorund Skalar-Ladeinstruktionen getestet. Abbildung 11 zeigt das Verhalten bei verschiedenen Problemgrößen. In Abbildung 11b ist zu sehen, dass die Bandbreite beim Schreiben immer erreicht wird. Zudem existiert kein Unterschied in der Schreibrate bei skalaren Instruktionen für TCM und SRAM. Allerdings wird die Bandbreite beim Lesen nicht erreicht, wie Abbildung 11a zeigt. Vielmehr ist ein kompletter Einbruch der Leserate zu

$<sup>^{19}\</sup>mathrm{Vgl.}$  Alif Semiconductors, Datasheet Ensemble Family E7 Series v2.11, S. 23.

<sup>&</sup>lt;sup>20</sup>Vgl. Alif Semiconductors, Datasheet Ensemble Family E7 Series v2.11, Table 5-14, S. 137.

<sup>&</sup>lt;sup>21</sup>Vgl. Alif Semiconductors, Datasheet Ensemble Family E7 Series v2.11, S. 36.

- (a) Lesedurchsatz für TCM und SRAM0

- (b) Schreibdurchsatz für TCM und SRAM0

Abbildung 11: Test des Lese- und Schreibdurchsatz auf TCM und SRAMO. L1-Cache als schwarze Linie eingezeichnet.

sehen, sobald die Problemgröße über den L1-Cache hinauswächst. Danach werden die angegebenen 1350 MB/s auch nicht erreicht, sondern nur 1176 MB/s. Weitere Tests wurden mit verschiedenen Cache-Attributen durchgeführt, welche allerdings keine Verbesserung bei den Leseraten gebracht haben. Außerdem ist zu sehen, dass das Laden mittels Helium-Instruktionen immer schneller ist, insbesondere aber in Fällen, wo ein hoher Durchsatz erreicht werden kann, da dort die volle Bandbreite von 64 Bit ausgeschöpft werden kann. Nicht abgebildet ist der Durchsatz auf dem HE-Kern, da dort das gleiche Verhalten auftritt.

### 3.2.3. Schneller Speicher - Tightly Coupled Memory

Der TCM-Speicher ist ein nah an die CPU angebundener Teil des SRAM-Speichers, der als besonders schneller Speicher fungiert. Dafür wird der TCM auf dem Ensemble E7 mit der Frequenz getaktet, mit der auch die angrenzende CPU getaktet ist. Für den HP-Kern bedeutet dies eine Frequenz von 400 MHz und für den HE-Kern eine Frequenz von 160 MHz. Dabei sind auf dem HP-Core der SRAM2-Bereich als Instruktions-TCM (ITCM) und SRAM3 als Daten-TCM (DTCM) eingebunden, wobei SRAM2 256 KB und SRAM3 1024 KB groß sind. Auf dem HE-Core sind beide SRAM-Bereiche 256 KB groß. Für den ITCM gibt es jeweils eine 32-Bit-Schnittstelle, die es unterstützt, pro Zyklus eine Instruktion zu laden, während es für den Zugriff auf den DTCM jeweils vier Schnittstellen D0TCM bis D3TCM gibt (siehe Abbildung 2 in 2.1.1).<sup>22</sup> Jede dieser vier Schnittstellen greift dabei mittels Adressfilterung nur auf bestimmte Speicherbereiche zu. Anhand von Bit 2 und 3 der Speicheradresse wird entschieden, welche Schnittstelle genutzt wird. Dabei wird für 0b00 die D0TCM-, für 0b01 die D1TCM-, für 0b10 die D2TCM- und für 0b11 die D3TCM-Schnittstelle genutzt. Diese Auswahl sorgt dafür, wie Abbildung 12 zeigt, dass bei FP32-Werten für jeden nachfolgenden Wert eine andere Schnittstelle genutzt wird. Dadurch kann die maximale Bandbreite von 64 Bit beim Nutzen von Vektor-Ladeinstruktionen, die 128 Bit innerhalb von zwei Zyklen laden, theoretisch erreicht werden.

Von Alif wird angegeben, dass eine Bandbreite von 3200 MB/s (1280 MB/s) erreicht werden kann.<sup>23</sup> Mit dem Microbenchmark aus 3.2.2 wird dies überprüft. Wie in Abbildung 11 zu sehen ist, wird die angegebene Bandbreite sowohl beim Lesen als auch beim Schreiben für HP- und HE-System erreicht.

<sup>&</sup>lt;sup>22</sup>Arm Ltd., Cortex-M55 Technical Reference Manual, S. 193

<sup>&</sup>lt;sup>23</sup>Vgl. Alif Semiconductors, Datasheet Ensemble Family E7 Series v2.11, Table 5-15, S. 137.

Abbildung 12: Nutzung verschiedener Schnittstellen im D-TCM beim Laden von FP32-Werten. Unten abgebildet sind die letzten vier Bit der zu den Werten gehörenden Speicheradressen.

Wie bereits geschrieben, wird bei Nutzung des TCMs der L1-Cache der CPU umgangen. Wie zu sehen ist, ist dieser auch gar nicht nötig, da der Durchsatz so hoch ist wie beim Cache. Der TCM ist somit optimal für performance-kritische Daten und Programmcode.

# 4. Just-In-Time-Kompilierung für Matrixmultiplikation

Um die Matrixmultiplikation für verschiedene Größen optimal auszuführen, soll der Matrixkernel programmatisch für eine angegebene Größe erstellt werden. Dazu ist es nötig, dass man ihn "Just in time" (JIT) generiert. Dafür werden Assembler-Instruktionen in einen Speicherbereich abgelegt, ein Zeiger auf den Speicherbereich abgespeichert und der Zeiger in eine Funktion konvertiert. Will man die Matrixmultiplikation ausführen, ruft man die Funktion an diesem Zeiger auf. Dies ist mit verschiedenen Herausforderungen verbunden, denn einerseits braucht man einen Speicherbereich, in dem die Instruktionen abgelegt werden können. Dieser Speicher muss entweder schnell sein oder mit Caches angebunden, so dass die Instruktionen in den Instruktions-Cache gelegt werden können. Ist das der Fall, muss die Anzahl der Instruktionen außerdem klein genug sein, damit sie in den Instruktions-Cache passen, da sonst performance-beeinträchtigende Cache-Misses auftreten. Außerdem müssen Berechtigungen gesetzt werden, damit auch Programm-Code aus diesem Speicherbereich ausgeführt werden kann. Für Embedded Systeme mit Armv8.1M-Architektur bestehen außerdem weitere Probleme, die im Folgenden beschrieben werden.

#### 4.1. Just-In-Time-Kompilierung auf Cortex-M55

Um JIT kompilierten Code auszuführen, benötigt man einen Speicherbereich, aus dem der Code ausgeführt werden kann. Auf modernen Linux-Systemen existiert dafür die Funktion map mit der man sich einen Speicherbereich zusichern und die benötigte Schreibbberechtigung auf ihn setzen kann. Mit der Funktion mprotect kann im Anschluss die Ausführ-Berechtigung gesetzt werden, nachdem die Instruktionen in den Speicherbereich kopiert wurden. Auf Embedded Hardware wie dem Ensemble E7 sieht die Situation allerdings anders aus: Hier gibt es keine Speicherverwaltungseinheit, die virtuellen Speicher verwaltet und kein Betriebssystem, mit dem man Speicher allozieren kann. Jeglicher Speicherzugriff erfolgt direkt auf den Speicher und die Konfiguration der Berechtigungen erfolgt über das Linker-Skript. Im Standard-Linkerskript für den Ensemble E7 sind alle Speicherbereiche bereits mit Schreib- und Ausführberechtigung konfiguriert. Dies bedeutet, dass man seine Instruktionen in ein Array schreiben kann und die Instruktionen durch Aufruf des Zeigers ausführen kann. Durch das Linkerskript kann außerdem bestimmt werden, in welchem Speichersegment der Code gespeichert werden soll, wobei der SRAM0 mit zusätzlichen L1-Cache sowie der TCM-Speicher zur Verfügung stehen. Zusätzlich zu den Standardseg-

menten werden für die JIT-Kompilierung die Segmente itcm\_jit im ITCM und sram0\_jit im SRAM0 im Linkerskript angelegt.

Wie aus den vorigen Abschnitten hervorgegangen, ist die Nutzung des TCM empfehlenswert, insofern genug Speicherplatz zur Verfügung steht. Dabei ist zu beachten, dass der Code, da in einem Array gespeichert, standardmäßig im Daten-TCM abgelegt wird. Dieser wird zwar mit vier Schnittstellen angebunden, so dass eine 32-Bit-Instruktion und zwei 32-Bit-Werte geladen werden können, da aber die Schnittstellen jeweils nur bestimmte Adressen bedienen, kann es bei Übereinstimmung von Bit 2 und 3 der Adresse der Instruktion und Daten dazu kommen, dass eine Schnittstelle zwei Werte laden müsste, was zwangsläufig zu Verzögerungen führt. Also ist es nötig, den Code im Instruktions-TCM abzulegen. Dafür wird ein eigenes Segment itcm\_jit im Linkerskript konfiguriert. Wie auf Linux-Systemen ist es auch hier notwendig, nach dem Generieren von JIT-Code die Caches und die Instruktions-Pipeline zu leeren, da sonst beim Ausführen der Funktion möglicherweise veralteter Code ausgeführt wird, der sich noch im Cache befindet.

Wie in 2.2.3 beschrieben, ist es für optimale Performance erforderlich, die Helium-Instruktionen im Low-Overhead-Loop auf 4 Byte auszurichten. Da die Direktive .p2align bei JIT-Kompilierung nicht zur Verfügung steht, muss manuell vor jeder Schleife, in der dies benötigt wird, ein zusätzliches NOP eingefügt werden. Dies wird über eine Hilfsfunktion geregelt, die die Ausrichtung der jeweiligen Instruktion prüft und, wenn nötig, das NOP einfügt. Mittels Compiler-Direktiven kann sowohl die Ausrichtung der ersten Instruktion als auch das Speichersegment sichergestellt werden. Dadurch wird das Linkerskript angewiesen, den Codebuffer im jeweiligen Segment anzulegen und das erste Element auf 4 Byte auszurichten.

```

uint16_t buffer[INSTR_COUNT] __attribute__((section(".itcm_jit"), aligned(4)));

```

Zuletzt muss beachtet werden, dass beim Funktionsaufruf, d.h. das Springen zum Zeiger auf den Instruktionsspeicher, das Least-Significant-Bit (LSB) der Adresse auf Eins gesetzt werden muss, da die BLX-Instruktion, die für den Sprung zur Funktion zuständig ist, anhand dieses Bits entscheidet, in welchem Modus der Prozessor ab nun arbeitet. Von Armv8.1-M wird dabei der ARM32-Modus (LSB auf 0) und der Thumb-Modus (LSB auf 1) unterstützt. Der Cortex-M55 unterstützt nur den Thumb-Modus, womit das LSB auf Eins gesetzt werden muss, da es sonst zu einem Fehler kommt.<sup>24</sup> Auf die Adresse hat das LSB keine Einwirkung, da vom Prozessor das LSB automatisch auf Null gesetzt wird, wenn zur Adresse gesprungen wird.<sup>25</sup>

Tabelle 6 zeigt die Ergebnisse des Microbenchmarks zur Ermittlung der Peak-Performance nun ausgeführt mittels eines JIT-Kernels. Die Peak Performance kann, wie zu sehen ist, auch mittels JIT-kompilierten Code erreicht werden, egal in welchem Speichersegment der Code liegt. Zu Probleme kommt es erst, wenn SRAM0 genutzt wird und die benötigten Instruktionen größer als der Instruktions-Cache ist.

| Test            | FLOPS |

|-----------------|-------|

| Buffer im ITCM  | 1.599 |

| Buffer im DTCM  | 1.599 |

| Buffer im SRAM0 | 1.599 |

Tabelle 6: Peak Performance JIT

<sup>&</sup>lt;sup>24</sup>Vgl. Arm Ltd., Cortex-M55 Generic User Guide, S. 92.

$<sup>^{25}\</sup>mathrm{Vgl.}$  Arm Ltd., Armv<br/>8-M Reference Manual, E2.1.33, S. 1937.

Die richtige Wahl des Speichersegments ist insbesondere wichtig, wenn gleichzeitig Daten geladen werden. Tabelle 7 zeigt den Durchsatz beim Laden eines Arrays, welches im DTCM liegt. Hier kommt es, wie oben beschrieben, zu Konflikten mit den TCM-Schnittstellen, wodurch die Ausführung aus dem DTCM-Segment langsamer ist.

| Test                | $\mathrm{GB/s}$ |

|---------------------|-----------------|

| Durchsatz JIT ITCM  | 3.1904          |

| Durchsatz JIT DTCM  | 2.986           |

| Durchsatz JIT SRAM0 | 3.191           |

Tabelle 7: Nutzung von eigenem Speicherbereich für JIT-Code

# 4.2. Umsetzung und Schnittstelle

Der JIT-Compiler muss es erlauben, Instruktionen zum Buffer hinzuzufügen, sowie Hilfsmethoden für den Programmfluss bereitstellen. Außerdem werden Methoden zum Enkodieren der verschiedensten Instruktionen benötigt. Dieser Abschnitt zeigt die Schnittstelle des JIT-Compilers, sowie die Verwaltung des Buffers. Abschnitt 4.3 beschreibt die Enkodierung von Instruktionen während Abschnitt 4.4 die Umsetzung von Branchinginstruktionen und Schleifen zeigt.

Das Backend ist als eigene Klasse konzipiert, der bei Instanziierung ein globaler Buffer zusammen mit seiner Größe übergeben werden muss. Es ist nicht möglich, einen als privat deklarierten Buffer in der Klasse zu nutzen, da dort keine Compilerattribute für das Setzen des Segments angegeben werden können. Das Backend wird von Generator-Klassen genutzt, von denen jede einen oder mehrere Kernel erzeugen. Für die Matrixmultiplikation wird dafür der GEMM-Generator genutzt; für die vorangestellten Performancetests in 4.1 wurden eigene Generatoren genutzt. Der Generatorklasse wird ebenfalls der globale Buffer übergeben. Die Generator-Klasse kann dann folgendermaßen instanziiert werden:

```

JIT::Generators::Gemm gemmGen(buffer, INSTR_COUNT);

```

Jede Generator-Klasse implementiert mindestens eine Funktion generate, die einen Kernel generiert. Außerdem wird ein Typalias Func für die Funktion erstellt. In der generate-Funktion wird zum Schluss der Pointer auf die erste Instruktion zurückgegeben und zur Funktion konvertiert. Mit getThumbAddress wird im Backend die Adresse der ersten Instruktion angepasst, damit beim Branch auch der Thumb-Modus genutzt wird.

```

// Definition des Funktionstyps. Übergeben werden A, B und C

using Func = void (*) (float const *, float const *, float *);

// Rückgabe des Pointers als Funktion

return reinterpret_cast<Func>(backend.getThumbAddress());

return reinterpret_cast<uintptr_t>(instructions) | 0x1U; // Setzen des LSB für Thumb-Modus

```

Die generate-Funktion des Gemm-Generators unterstützt die Angabe der Matrixgrößen sowie ihrer "leading dimensions" lda, ldb und ldc, d.h. die Anzahl der Elemente die für A, B bzw. C übersprungen werden müssen, um zur nächsten Reihe zu springen. Die Funktion kann dann folgendermaßen genutzt werden:

```

// Buffer der Größe INSTR_COUNT übergeben

JIT::Generators::Gemm generator(buffer, INSTR_COUNT);

JIT::Generators::Gemm::Func testFunc = generator.generate(m, k, n, lda, ldb, ldc);

testFunc(A, B, C);

```

Es existieren Methoden, um Instruktionen zum Code-Buffer hinzuzufügen, außerdem existiert eine Methode, um eine Helium-Instruktion hinzuzufügen und korrekt im Speicher anzuordnen. Dazu wird beim Einfügen eine zusätzliche NOP-Instruktion eingefügt, falls die Instruktion ansonsten nicht auf 4 Byte ausgerichtet ist. Da auch 16-Bit-Instruktionen unterstützt werden, besteht der Code-Buffer aus uint16\_t-Werten, wobei ein Wert eine 16-Bit-Instruktion ist. Soll eine 32-Bit-Instruktion hinzugefügt werden, werden zwei 16-Bit-Werte hintereinander geschrieben, da die CPU anhand der ersten fünf Bits der Instruktion erkennt, ob es eine 32-Bit-Instruktion ist und dann gegebenfalls die nächsten 16 Bit aus dem Speicher lädt.<sup>26</sup>

## 4.3. Instruktionsenkodierung für Matrixmultiplikation

Es werden alle benötigten Instruktionen für Matrixmultiplikation implementiert. Dazu gehören mehrere Helium-Instruktionen, aber auch einige skalare Instruktionen, sowie Branchinstruktionen und Lade-/Speicherinstruktionen. Dabei sind für ein Großteil der Instruktionen sowohl die 16-Bit- also auch die 32-Bit-Varianten implementiert. Die übergebenen Parameter werden auf Richtigkeit geprüft; werden nicht unterstützte Parameter angegeben, wird eine Fehlermeldung ausgegeben und stattdessen ein NOP zurückgegeben. Somit kann geprüft werden, an welcher Stelle die falsche Angabe gemacht wurde. Es werden, wenn nötig, Immediate Constants<sup>27</sup> unterstützt. Bei der Umsetzung der verschiedenen Instruktionsenkodierungen wird sich nach den Bedürfnissen bei der Matrixmultiplikation gerichtet, sodass nicht alle Enkodierungen einer Instruktion unterstützt werden, sondern nur diese, die auch benötigt werden.

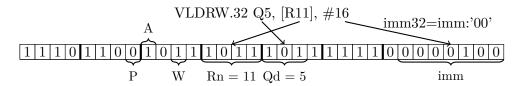

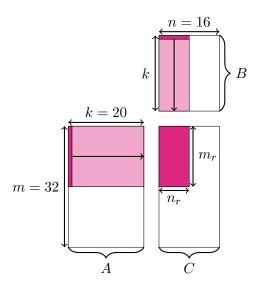

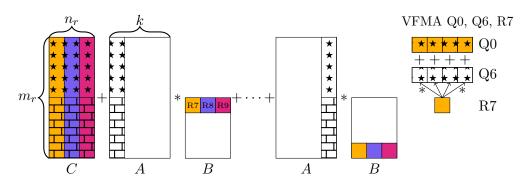

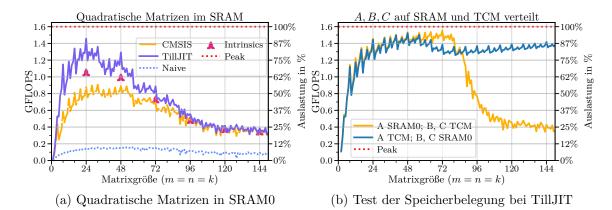

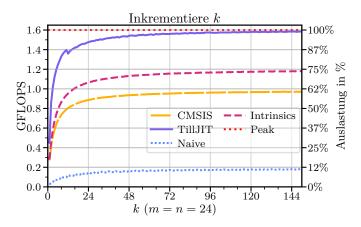

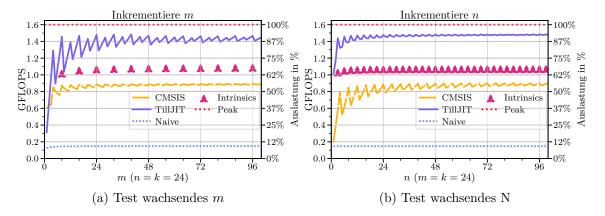

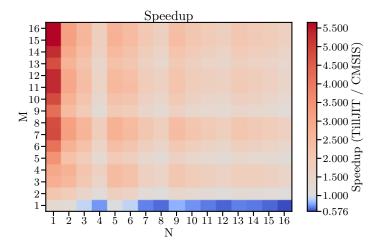

Abbildung 13: Enkodierung der VLDR-Instruktion